Cadence Documentation

1. Cadence Documentation Survey

Cadence is committed to providing high-quality documentation. To help us shape the future of Cadence documentation delivery, we welcome you to complete our survey.

Application Notes

2. Virtuoso Spectre Transient Noise Analysis

This document discusses the theoretical background of the Spectre solution’s transient noise analysis, its implementation and implications, and the latest use model together with many useful simulation time-saving and circuit diagnostic features. Most importantly, this application note provides a very detailed tutorial example with the Virtuoso ADE environment, a few periodic steady-state circuits to show the correlation with periodic steady-state noise analysis (pnoise), and the use of transient noise analysis on its main application - nonlinear and non-periodic data converter designs.

3. Calibrated Verification with ADE XL

This application note focuses on one of the most important types of advanced analog and mixed-signal verification, which is verification in the calibrated condition. It provides explanations and examples of using ADE XL features such as the calcVal() function, Verilog-A blocks, and pre-run scripts.

4. Virtuoso Analog Design Environment XL: Variables, Sweeps and Corners

A "best practices" document covering topics on the use of variables, sweeps, device parameterization, corners setup, results filtering, datasheets, and spec comparison in ADE XL.

Rapid Adoption Kits

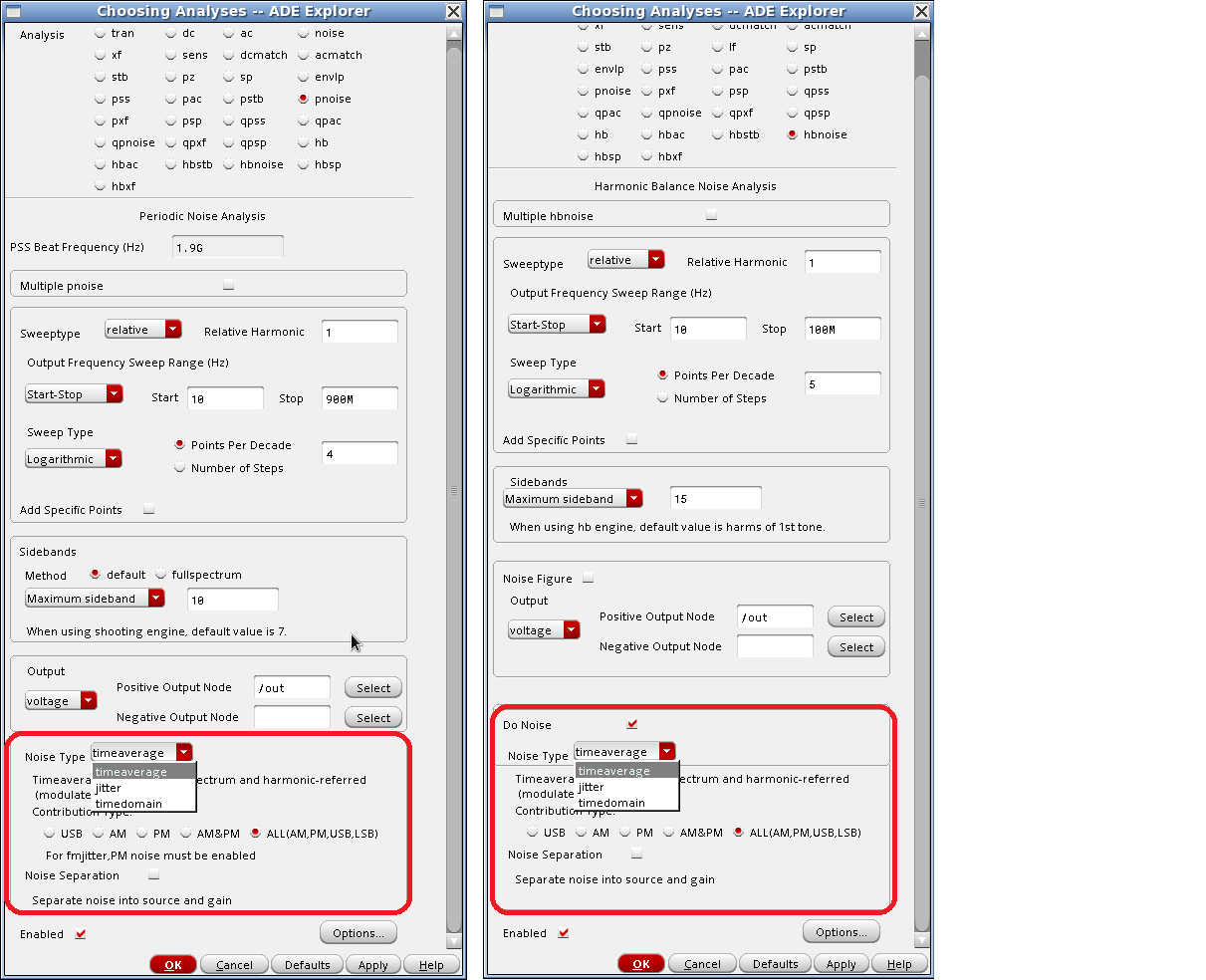

5. Jee Measurement Using PSS/Pnoise and Transient Noise Analysis

Jitter is a key measurement in systems where the periodic behavior or exact event timing is crucial to system performance. Various jitter metrics characterize the statistics of the observed sequence of events. This variation in the delay between a triggering event and a response event is the edge-to-edge timing jitter. It is also called as absolute or aperture jitter. This RAK demonstrates how to do Jee measurement using Pnoise and Tran noise.

Videos

6. Virtuoso Analog Auto Placer

This video discusses the basics of analog placer, capture design constraints in schematic, capture modgen constraints, and automatic placement using the analog placer.

In this video, you will see how to save and plot operating point parameters for transient and DC sweep analysis for Spectre simulator from ADE-L and ADE XL. It will also cover how to specify hierarchy levels to save subckt Instances in ADE L and ADE XL.

This video shows how to create a Pspice view and then perform Spectre-based netlisting by using this view.

Training Bytes

- Virtuoso Connectivity-Driven Layout Transition IC6.1.6

- Skill IDE

Blogs

9. EDPS 2015: Choosing FinFET, FD-SOI, or Bulk Planar FETs

If you’re designing an IC today, you have three types of transistors to choose from – traditional bulk planar FETs (down to 20nm), FinFETs (below 20nm), and FD-SOI (fully depleted silicon-on-insulator, 28nm). How can you make the best choice for your design? A session at the recent Electronic Design Process Symposium (EDPS 2015) provided a wealth of information to help you decide.

Solutions

10. How to Run a dc Without Saving dcOpInfo

You are running a dc simulation. You have save=selected in ADE. You are running on an extracted view. The dcOpInfo analysis that comes along with dc is very large and filling up your disk. Can you run dc without it?

11. New Spectre +dcopt Option to Help dc Convergence

You are running a large Spectre simulation and you are having trouble converging in dc. You have done all the suggestions printed in the spectre.out file after convergence failure. What else can you do?

12. VLS- XL: Cross Highlighting Net Between Layout and Schematic Window

In XL mode, when I select a net in the Virtuoso Schematic window, corresponding net gets selected on the layout side. However, it does not work vice versa. I am selecting a net (path segment) on the layout side; however, the corresponding net in the schematic is not getting selected. How can I get it to work?

13. Example of How to Use axlReadHistoryResDB to Access Scalar Result Database in ADE XL

You have run some simulations in ADE XL (either from the UI or using OCEAN XL), and want to know how to traverse the result database (the "RDB") to access the scalar results and information about the simulations performed. You have read the documentation on axlReadHistoryResDB and understand that this returns an object which you can traverse points, corners, outputs and so on - and it has built-in help. However, you would like an example which iterates through all the results, giving information on the sweeps, the corners, the tests, and the outputs, structured in the correct order.

14. How to Restrict Spectre APS to Use the Number of Threads Reserved by LSF?

You are submitting Spectre APS simulation jobs on LSF. While submitting the job you are using +mt or +mt=8 and do not reserve the required cores using "-n " in the LSF command string. Due to this the LSF allocates a single core for the job, but Spectre APS ends up taking more than 1 core without any message. This results in affecting the other jobs that are running on the same machine. How can I restrict Spectre APS to use threads reserved by LSF?

Stacy Whiteman